# NAME: DERRI COLUMBUS BOMAYE

MATRIC NO: 15/ENG02/017

# DEPARTMENT: COMPUTER ENGINEERING

## COURSE CODE: COE506

### COURSE TITLE: DIGITAL DESIGN USING VHDL

#### ASSIGNMENT

#### **QUESTION ONE SOLUTION**

- i. **ASIC**: Application-Specific Integrated Circuit is an integrated circuit (IC) chip customized for a particular use, rather than intended for general-purpose use.

- ii. **PAL**: Programmable Array Logic is a commonly used programmable logic device (PLD). PAL consist of small programmable read only memory (PROM) and additional output logic used to implement a particular desired logic function with limited components.

- iii. PLA: Programmable Logic Array is a kind of programmable logic device used to implement combinational logic circuits. The PLA has a set of programmable AND gate planes, which link to a set of programmable OR gate planes, which can then be conditionally complemented to produce an output.

- iv. **PLD**: Programmable Logic Device is an electronic component used to build reconfigurable digital circuit. Unlike integrated circuit (IC) which consist of logic gates and have a fixed function, a PLD has an undefined function at the time of manufacture.

- v. **CPLD**: Complex Programmable Logic Device is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The main building block of the CPLD is a macro cell, which contains logic implementing disjunctive normal form expressions and more specialised logic operations.

- vi. **FPGA**: Field-Programmable Gate Array is an electronic component used to build reconfigurable digital circuits. That means that an FPGA is different from a logic gate, because logic gate has a fixed function. FPGAs are integrated circuits in the category of programmable logic devices or PLDs.

## **QUESTION TWO SOLUTION**

Granularity of logic block has influence on performance of an FPGA. Typically, higher granularity levels result in lesser delay between input and output. As the granularity of logic block increases, the number of levels of logic in critical path decreases, and hence delay in critical path decreases.

# **QUESTION THREE SOLUTION**

- a) The devices typically offer a higher degree of integration as compared to discrete 7400-series or 4000-series components. They're smaller, and use less power. In some cases, they're re-programmable, allowing upgrades without changing the PCB. By the time you get to FPGAs, you could have a truly massive amount of reprogrammable logic. It's simply infeasible to build that much logic in discrete components. And if you want to build a custom hardwired ASIC instead, you could be on the hook for millions.

- b) Yes, many.

In the embedded world where electronics are being controlled there are many places where a hard wired solution is the only way to go as there is a critical timing constraint. Working on a motor controller where the current in the coils has to be measured controlled, real time, in nanoseconds whilst other measurements and algorithms are being calculated. This is easy to do in hardwire, but impossible to do with current chips in software. Short of very expensive CPUs that would still have difficulty in achieving the timing constraints, a hard wired solution is the only answer.

Some of the embedded processors available today have ability to 'hardwire' digital, analog, and FPGA components as part of their offering. You end up with hard wired logic and function that is defined by software within a single chip. The 'hard wiring' is reconfigurable in development but can be locked in production. This is sometimes done by a configurable 'mask' at the end of the chip manufacturing process. The hard wiring is then truly 'hard' and impervious to neutron and magnetic bombardment. Such chips cannot be upgraded in the field.

## **QUESTION FOUR SOLUTION**

Certainly, the stored program will be non-volatile, but it will also be read-only. This is why fuse-programmed devices are sometimes called OTP. OTP (one time programmable) memory is a special type of non-volatile memory (NVM) that permits data to be written to memory only once. Once the memory has been programmed, it retains its value upon loss of power (i.e., is non-volatile). OTP memory is used in applications where reliable and repeatable reading of data is required.

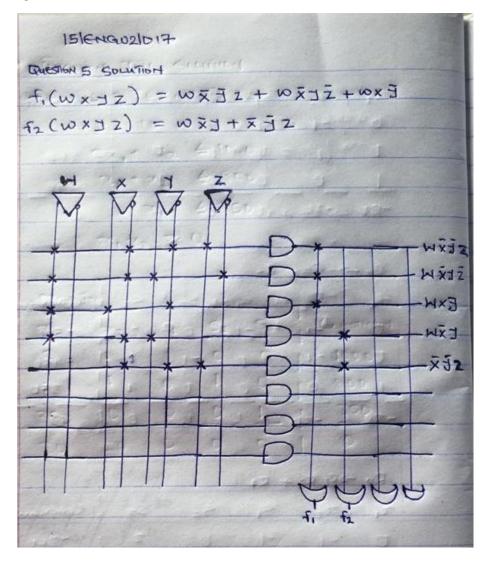

# **QUESTION FIVE SOLUTION**